SMD的9种封装技术介绍【图文】

表面组装器件(SMD)是在原有双列直插器件(Dual in-line Package,DIP)的基础上发展起来的,是通孔插装技术向SMT发展的重要标志,表面组装器件主要有以下9种封装技术。

(1)小外形晶体管 (SOT) (small outline transister)

SOT是采用小外形封装结构的表面组装晶体管,主要有SOT23、SOT89、SOT143、SOT25等。SOT23是常用的三极管封装形式,有3条翼形引脚,分别为集电极、发射极和基极,分别列于元件长边两侧,其中,发射极和基极在同一侧,常见于小功率晶体管、场效应管和带电阻网络的复合晶体管,强度好,但可焊性差,外形如图2-1(a)所示。SOT89具有3条短引脚,分布在晶体管的一侧,另外一侧为金属散热片,与基极相连,以增加散热能力,常见于硅功率表面组装晶体管,适用于较高功率的场合,外形如图2-1(b)所示。SOT143具有4条翼形短引脚,从两侧引出,引脚中宽度偏大的一端为集电极,这类封装常见于高频晶体管,外形如图2-1(c)所示。SOT252属于大功率晶体管,3条引脚从一侧引出,中间一条引脚较短,为集电极,与另一端较大的引脚相连,该引脚为散热作用的铜片。外形如图2-1(d)所示

(a) |

(b) |

(c) |

(d) |

图2-1 SOT外形图

(2)小外形封装集成电路(SOIC) (small outline Integrated Circuit )

SOIC封装为两侧有翼形状或J形状短引线的一种表面组装元器件封装形式。SOIC封装有两种不同的引脚形式:一种是翼形引脚的SOP,一种是具有J形引脚的SOJ。

SOP封装常见于线性电路、逻辑电路、随机存储器等,常见的型号有SOP8、SOP14 SOP16、SOP20、SOP24、SOP28、SOP48、SOP56、SOP64等。SOP引脚间距有1.27mm、1.0mm、0.65mm、0.5mm、0.4mm、0.3mm等,引脚数为双数,对称分布。

SOJ与SOP不同,其引脚间距只有1.27mm,引脚数主要有14、16、18、20、22、24、26、28。与翼形引脚相比,J形引脚比较粗,不易变形,J形引脚具有一定的弹性,可以缓解贴装和焊接的压力,防止焊点开裂。

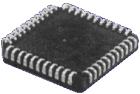

(3)塑封有引脚的芯片载体PLCC(Plastic Leadled Chip Carrier)

PLCC封装的引脚在芯片底部向内弯曲,J形引脚具有一定的弹性,可缓解安装和焊接应力,主要用于计算机微机处理单元、专用集成电路、门阵列电路等。PLCC有方形和矩形两种,方形的引脚数有20-84个,矩形的引脚数有18-32个,其外形如图2-2所示。

|  |

图2-2 PLCC外形图

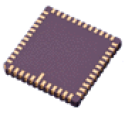

(4)无引脚的陶瓷芯片载体LCCC(Leadless Ceramic Chip Carrier)

LCCC是在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装,芯片被封装在陶瓷载体上,用于高速,高频集成电路封装,引脚间距主要有1.27mm和1.0mm两种。LCCC外形有正方形和矩形两种,正方形有16、20、21.27mm和1.0mm两种。LCCC外形有正方形和矩形两种,正方形有16、20、24、28、44、52、68、84、100和156个电极,矩形有18、22、28和32个电极,其外形如图2-3所示。

图2-3 LCCC外形图

(5)方形扁平封装(QFP)(Quad flat package)

QFP是适应集成电路内容增多、I/O数量增多而出现的封装形式,是专门为小引脚间距IC而研制的新型封装形式。QFP四边都具有翼形短引脚,封装的芯片一般都是大规模集成电路,有方形和矩形两种,电极引脚数最少为28脚,最多可达到576脚,常见的引脚间距有1.0mm、0.8mm、0.65mm、0.50mm、0.40mm、0.3mm等,QFP由于引脚多,接触面积大,具有较高的焊接强度,但在运输、存储和安装中引脚易折弯和损坏,使引脚的共面度发生改变,影响器件的共面焊接。

随着封装技术的不断发展,目前市面上已有收缩型四方扁平封装(SQFP),薄型

四方扁平封装(TQFP)和陶瓷四方扁平封装(CQFP)等形式,他们的尺寸比传统的QFP更小,其中TQFP封装的厚度已经降到1.0mm甚至0.5mm。

(6)球栅阵列封装BGA(Ball Grid Array)

BGA是大规模集成电路的封装技术,封装的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,常见的引脚间距有1.5mm、1.27mm、1.0mm。BGA封装I/O引脚数虽然增加了,但引脚间距并没有减小反而增加了,从而提高了组装成品率,虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,从而可以改善它的电热性能,厚度和重量都较以前的封装技术有所减少,信号传输延迟小,使用频率大大提高,组装可用共面焊接,可靠性高,极大地改善了组装的工艺性,特别适合在高频电路中使用。存在的问题是焊后检查和维修比较困难,必须使用射线检测才能确保焊接的可靠性;易吸潮,使用前应经过烘干处理。

BGA通常由芯片、基底、引脚和封壳等组成,根据芯片位置、引脚排列、基底材料和密封方式的不同,BGA可分为塑封球栅阵列(Plastic Ball Grid Array,PBGA)、陶瓷球栅阵列(Ceramic Ball Grid Array,CBGA)、陶瓷柱栅阵列(Ceramic Column Grid Array,CCGA)和载带球栅阵列(Tape Ball Grid Array,TBGA)等。

PBGA芯片正面朝上,通过金线压焊到基底的上表面,封装成本低,引脚不易变形,可靠性高,易吸湿,拆下后须重新植球;CBGA是连接在多层陶瓷基底的上表面,电性能、热性能、机械性能高,抗腐蚀、抗湿性能好,但封装尺寸大时,陶瓷与基体之间的CTE失配,易引起热循环失效;CCGA焊料柱可承受元器件、PCB之间不同而产生的应力,组装过程中焊料柱比焊球更易受机械损伤;TBGA采用双金属层带作为其基底,基底与芯片之间的连接通常用倒装技术来实现,体积小,电性能优异,易批量组装,与PCB的CTE匹配性好,但易吸湿,封装费用高。

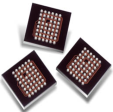

(7)芯片尺寸级封装(Chip Scale Package )

CSP是BGA进一步微型化的产物,它减小了芯片封装外形的尺寸,封装后的IC尺寸边长不大于芯片的1.2倍,IC面积不超过晶粒的1.4倍,适用于引脚数少的内存条和便携式电子产品,常用的引脚间距有1.0mm、0.8mm、0.65mm、0.5mm,其外形如图2-4所示。

图2-4 CSP外形图

CSP比QFP提供了更短的互连,电性能更好,更适合在高频场合使用,尺寸比BGA更小,更平整,有利于提高回流焊质量,本体薄,故具有更好的散热性能,但是存在焊点质量检测问题和热膨胀系数匹配问题。

(8)裸芯片封装COB(Chip on Board)

COB是将裸芯片用导电或非导电胶粘附在互连基板上,然后进行引线键合实现其电气连接,焊区与芯片体在同一平面上,周边均匀分布,最小间距为0.1mm,采用线焊将引线和PCB焊盘焊好,用环氧树脂进行封装保护键合引线。

COB不适合大批量自动贴装,并且用于COB法的制造工艺难度相对较大,散热也有一定困难,通常适用于低功耗的IC芯片,其外形如图2-5所示。

图2-5 COB外形图

(9)倒装芯片封装FC(Flip Chip)

倒装芯片封装技术为1960年IBM公司所开发,为了降低成本,提高速度,提高组件可靠性,FC使用在第一层芯片与载板接合封装,封装方式为芯片正面朝下向基板,无需引线键合,形成最短电路,降低电阻;采用金属球连接,缩小了封装尺寸,改善电性表现,解决了BGA为增加引脚数而需扩大体积的困扰。

FC通常应用在时脉较高的CPU或高频RF上,以获得更好的效能,与传统速度较慢的引线键合技术相比,FC更适合应用在高脚数、小型化、多功能、高速度趋势IC的产品中。